The inaugural

Global Interposer Technology Workshop (GIT) was recently held on the campus of GIT (Georgia Institute of Technology). While we usually report on conferences based on numbers of attendees and presentations, Karen May, GaTech coordinator of the conference, had a much more interesting measuring stick -- reporting that the 138 attendees consumed 106 gallons of coffee, 83 pounds of pasta, and 12 dozen ice cream sandwiches. Over the next few blogs I will try to update you on what was presented and what was said. Several of the presenters (it will be obvious which ones) did not want their slides released, so in those instances I will be going from my handwritten notes.

While every conference even remotely linked to microelectronics feels pressure to have at least one session dealing with 3D integration, this workshop was started, and appears to be unique, in that it's focus is solely on 2.5D i.e. interposers.

Row 2 (L-R): Swaminathan (GIT), Nopper (ST Micro), Sukumaran (GIT), Franzon (NC State), Huemoeller (Amkor), Matthias (EVG), Salmon (Semi), Kumbhat (GIT), Dunne (TI) ; Row 1 (L-R): Kitaoka (AGC), Ramalingam (Xilinx), Garrou (Assist Chair), Tummala (Chair), Dunne (TI)

Suresh Ramalingam -- Xilinx

Suresh Ramalingam -- Xilinx

Certainly the highlight of the conference was Xilinx due to their highly publicized announcements on their Virtex 7 2000T FPGA, which uses a 21mm x 26 mm TSV interposer, which they have been sampling since September, and will have in full production in 2012. For details on the previous Xilinx announcements see [

IFTLE 73, "

Xilinx shows 2.5D Virtex 7 at IMAPS 2011" and

IFTLE 23, "

Xilinx 28nm multidie FPGA..."]. TSMC is fabricating the chip and the interposer, Amkor is bumping the chip and assembling the FPGA slices on the interposer, and Ibiden is fabricating the package substrate. Ramalingam emphasized that the interposer solution was necessary (vs. full 3D stacking) to insure proper thermal performance.

Increasing demand for FPGA capacity is reportedly coming from:

- Wired communications

- Image and video processing

- ASIC prototyping, emulation and replacement

All applications are constrained by the devices overall power budget and thermal concerns.

Full reliability qualifications are almost complete.

Future products are expected to be heterogeneous combinations such as the FPGA slices + SERDES chips shown below.

Doug Yu -- TSMC

If the highlight was Xilinx, then the headline was TSMC, which concerning 3D and 2.5D has been very careful about what they say and how they are saying it -- thus the comments made by Yu at this meeting drew great attention. Yu, Sr Director of Integrated Interconnects and Packaging at TSMC had some significant comments on 2.5D interposer supply chain developments. While there have been many recent proposals for how module fabrication tasks would be divided between foundries, IDMs, OSATs, and possible 3rd-party interposer suppliers, Yu proposed that for now, the interposers should be built completely by one party to define clear ownership and an efficient route to cost and yield improvements. Yu proposes that the foundries which can leverage their Cu processing capability, offer no customer competition (vs. IDMs), and have the design support capabilities would be the natural source for interposers. Furthermore, at several points during the two-day meeting, Yu reiterated that this is TSMC's plan. However, you should also know that rumors in the audience indicate that TSMC is currently only engaging selected 1st-tier customers with their interposer technology, which should be no surprise. When asked when TSMC would be releasing their 2.5D ground rules, Yu indicated that TSMC does not release their ground rules for any of their processes except to their partner/customers.

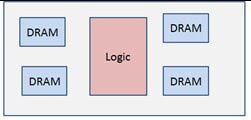

While everyone knows that TSMC is engaged with Xilinx on bringing their FPGA product to commercialization, it was of great interest to see Yu commenting that they were also working on mixed-chip solutions (like the memory + logic depicted below ) using interposers with 10um x 100um TSV).

Bryan Black -- AMD

Bryan Black -- AMD

Byran Black, CTO of AMD, indicated that AMD is taking a "very broad view of TSV and stacking" and that the industry "will stagnate if we don't get 3D." While Black claims that AMD has been involved in 3D for more than five years, he added that they are "intentionally not talking about what we're doing."

Most of us remember Black from his days at Intel. In the early 2000's he was already publishing seminal 3D papers including "

3D Processing Technology and Its Impact on iA32 Microprocessors" [

Proc. IEEE Int. Conf. on Computer Design, pages 316-318, 2004]

IFTLE should note that a similar "stealth" approach was taken by Micron until its recent announcements concerning its memory cube technology -- see

IFTLE 74, "

HMC -- TheMemory Cube consortium."

The audience certainly took notice when Black stated that the "Southbridge" was probably the last AMD chip that would be impacted by scaling. He envisions that in the future chip companies will be focusing process node development on specific application functionalities. He contends this will reduce mask layers and run time and increase yield, while improving performance and reducing power requirements, area, and cost for each individual functionality. These separately fabricated functionalities would then be combined vertically and/or horizontally on an interposer to form the final circuit function.

Paul Franzon -- NC State

Paul Franzon -- NC State

Paul Franzon, Professor of EE at NC State and long time 3D practitioner, compared the capabilities of SoC vs. 2.5D vs. 3D, agreeing that thermal performance was the outstanding feature of 2.5D as shown below. He reiterated, as many others have, that performance is often limited by memory capacity and bandwidth.

Franzon detailed the concept of "dark silicon" where most of the chip must be in "off mode" at any given time to meet predetermined power budgets. Low-power 2.5 and 3D solutions are expected to alleviate this situation.

Franzon also concluded that stacking processor on memory would allow the processor temperature to be better controlled by attachment to the capping heat sink, but would not offer enough temperature differential to the memory underneath the processor which is in intimate contact. This differential is much better when using an interposer. [See a similar discussion by LSI in

IFTLE 77, "

MEPTEC 2.5, 3D and beyond."]

We'll finish up GIT @ GIT next week and then cover IEEE IEDM and RTI ASIP -- plenty of important 3D news is coming your way in the next few weeks!

Also don't forget to enter our

IFTLE contest --

see IFTLE 78 for details!

For all the latest in 3DIC and advanced packaging stay linked to

IFTLE..........