Bill Bottoms, CEO of 3MTS gave the introductory talk taking a look a collaborative roadmaps and international roadmap perspectives. From his position as chair of the ITRS (Int Technology Roadmap for Semiconductors) packaging and assembly TWG (technical working group) Bill reminded attendees that ITRS is sponsored by Europe, Japan, Korea, Taiwan and the US to:

- forcast semiconductor technology requirements 15 years out and

- forcast emerging semiconductor devices and materials 10 years out

Its relationship to other Microelectronic roadmap activities in the US is shown below where i-NEMI is actually the pivot point for all the microelectronic activities.

On a global basis, the other organization looking at overall semiconductor packaging solutions is JISSO [link], a Japanese term which reflects the total packaging solution for electronic products. The chart below shows its relationship to other global standards organizations.

Bottoms premise is that for the past 40 years semiconductor progress could be easily predicted. The focus was on design and fab. Semiconductor roadmap goals were all clearly focused on shrinking geometries (scaling) and increasing wafer size. However, as we enter the “deep submicron” era, however, things become more complicated and packaging becomes a more important in delivering semiconductor yield, reliability and performance.

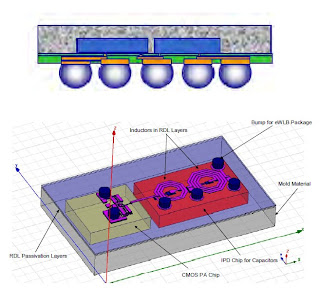

The answer developed to adress the historical lack of package scaling to match IC scaling was to generate the packaging at the wafer level, i.e. wafer level packaging or WLP. WLP, now firmly entrenched as a packaging option offers portable consumer products :

- inherently lower cost

- better electrical performance

- lower power requirements

- smaller size

Several architectural variations of WLP are in use today as are shown below.

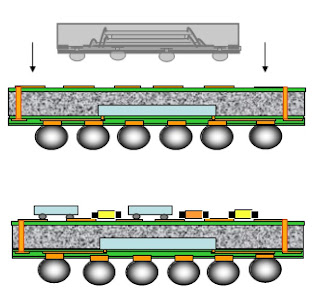

Another important trend in packaging is the incorporation of multiple die into a single package or what has become known as System in Package (SiP) [ MCM to those of us that have been around awhile].

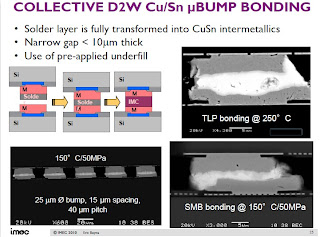

Moving forward, Bottoms predicts, as many of us do, that the 3rd dimension will be the key enabler in maintaining the “price elastic growth of the electronics industry”. While 3D presents many challenges they all appear to have reasonable solutions. 3D will appear first through silicon interposers with through wafer connections and then through chips fabricated with internal TSV for through wafer connections .

Bill updated attendees with where the packaging roadmap would be increasing and expanding coverage in 2011. [ see “Packaging, assembly changes coming in next ITRS Update” ]

Bottoms concludes that the pace of change in packaging technology has never been greater and roadmaps are critical to continuation of this rate of progress.

Bryan Black of AMD looked at why 3D is required if semiconductor technology is to continue to move ahead. In standard fashion Black defines 3D technology in two varieties as shown below, TSV in active devices and TSV on interposers.

From a systems standpoint Black proposes the interesting perspective that performance density drives new form factors, new form factors discover new usage models and without new form factors the industry would stagnate. This trend is shown in the slide below:

For all the latest on 3D integration and advanced packaging stay linked to IFTLE…..