……….Finishing our look at the 3D related events at the recent Semicon West exhibition.

EVG

Markus Wimplinger , Corp Tech and IP Director, shared that 3D and TSV have been a main focus for EVG during the downturn and they feel these technologies have served them very well financially.

Wimplinger sees the only 300 mm 3D line in production is the ST Micro CIS (CMOS Image Sensor) line. Line qualification is underway right now for several customers who should be finished by 4Q 2010. He predicts that some but not all of their customers will be ready for production in the 2011-2012 timeframe and that most of them will be in Asia. Those that are furthest along actually have process ground rules out to selected key customers but have not widely distributed them yet. He also notes that W2W bonding is on the upswing again after bottoming out (vs D2W) around 12 months ago.

Verigy

Mark Allison, VP of strategic Marketing indicated that Verigy is a member of both the IME (Singapore) and ITRI (Taiwan) 3D consortia. Allison reported that some of their customer base were exerting pressure for 3D IC test solutions while others appeared to be waiting to see further clarity in the infrastructure.

Some of the TSV test challenges that they have found include:

- TSV size vs probe capabilities

- making sure the DFT (design for test) probe pads don’t add capacitance and inductance to the TSV

- handling the complex functionality of the stack

Verigy is looking into putting DFT structures on interposer which is lower cost real estate.

Equipment Heavyweights Have a Change of Heart

In the past few years PFTLE and IFTLE have documented the move of Equipment heavyweights Applied Materials and Novellus into the here-to-fore shunned area of packaging. [See PFTLE 72 “Samsung 3-D ‘Roadmap’ That Isn’t”, 4/16/2009; IFTLE “...on Finding the Beef and Finally Addressing 3D IC”, June 2010]

It wasn’t so long ago that such heavyweights snubbed their nose at the packaging market. Well, the upcoming end to scaling and Moore’s Law (as we know it) sure have turned things around [ see PFTLE “IC Consolidation, Node Scaling and 3D IC”, 03/03/2010]. Topics like 3D TSV and WLP are now the darlings of the equipment industry.

Don’t get me wrong, having the big boys set their sights on packaging and 3D with TSV is positive and developments that they come up with can only improve things for all of us in the long run. With reports that 300 mm 3D lines are going intro place around the world “as we speak” it was to be expected that both would be in “full court press” mode at Semicon – and they were.

AMAT

Dr. Randhir Thakur, executive vice president and general manager of Applied’s Silicon Systems Group announced that Applied could now offer customers “...a complete toolset for all TSV manufacturing flows encompassing etch, CVD, PVD, ECD, wafer cleaning and CMP,” said. , Applied’s Maydan Technology Center and their activity at institutes like IMEC and ITRI can only help customers develop “.. a smooth transition from R and D to volume production” as they put it.

Novellus

Novellus introduced new models of the company's VECTOR PECVD, INOVA PVD, and GxT photoresist strip systems specifically designed for WLp and 3D.

The newly-introduced SABRE 3D system addresses void-free filling, reduced copper overburden, and improved fill uniformity at higher throughputs. SABRE 3D's modular architecture can be configured with multiple plating and pre-or-post-treatment cells for a variety of packaging applications including TSV, pillar, RDL, under-bump metallization, and eutectic and lead-free micro-bumping using materials such as copper, tin, nickel, and tin silver.

The INOVA 3D PVD reportedly provides “...superior copper sidewall coverage and ultra-low defects in high aspect ratio TSVs”. The ion-induced PVD approaches reportedly reduces the manufacturing cost of consumables for the TSV PVD process step by greater than 50 percent.

The VECTOR 3D system is reportedly able to deposit low-temperature films such as silicon nitride diffusion barriers and silicon oxide isolation and passivation layers.

The G3D photoresist strip system has been designed to quickly remove thick (20-100 micron) photoresists used in the manufacture of RDLs and pillars and to achieve residue-free strip and clean of high aspect ratio TSVs.

FPGA 3D IC Rumors

With their highly repetitive structure, FPGAs have been a natural application space for 3D IC technology although no details have been announced or published anyone on the subject. Recently there have been rumors of real work going on out there that I would be remiss I not sharing with you.

In June, in his blog on chip design magazine (link), Ed Spurling reported that although Xilinx refused to comment, “a half dozen industry sources familiar with its efforts” reported that Xilinx is developing 3D for its FPGAs. IFTLE will take it one better than that and report to you that the rumored site for Xilinx activities is Samsung. No proof here either, and no confirmation from either party just the strong rumor. Although Samsung remains deathly silent on all activities concerning 3D, trust me they will be a player.

For all the latest in 3D IC and advanced packaging technology, news and rumors stay linked to Insights From the Leading Edge, IFTLE...

Friday, August 27, 2010

Friday, August 20, 2010

IFTLE 12 3D at the DAC , 3D Survey at the GSA

The importance of of suitable design tools for 3D IC have been detailed previously [ see IFTLE 9 “3D In and Around the Moscone Part 1”, Aug, 2010; PFTLE 102 The 4 Horsemen of 3D IC”,10/16 2009; PFTLE 70 “Deep in the Heart of Texas” 04/04/2009 ].

Well, it’s now becoming clear that significant EDA industry attention is being directed towards 3D IC technology.

The Design Automation Conference (DAC) which started in 1964 is clearly the preimminent technical conference / trade show, specializing in design automation. DAC is sponsored by several professional societies including IEEE Circuits and Systems Society, the IEEE Solid-State Circuits Society and the IEEE Council on Electronic Design Automation. The 2010 DAC was held in Anaheim CA.

This year, 3D IC design finally took a prominent position in the technical program. Rahul Deokar of Cadence called 2010 DAC "...a coming out party for 3D-IC design” (Link). Rick Nelson (Editor –in-chief of Electronic Design News) after attending the 3D activities at DAC writes that “the time is now for 3-D stacked die” and that “the consensus seems to be that the 3-D revolution is imminent.

Every once in awhile someone comes up with something cleaver where I think to myself “damn I wish I had thought of that” So hats off to Rick Nelson for his 3D clock (left). I’m sure I’ll be using this in future slide presentations, so in case I forget to give Rick credit, I’m doing so now in public.

In the first ever DAC panel session dedicated to 3D IC entitled "3D Stacked Die: Now or the Future?" included Myung-Soo Jang of Samsung, LC Lu of TSMC, Philippe Magarshack of ST Micro, Marchal Paul of IMEC and Riko Radojcic of Qualcomm. They all addressed the question "Are we (3D IC) there yet ?...Is it now or the future?"

There was a consensus among the speakers that commercial release of the first 3D memory on logic devices was imminent. (IFTLE feels this is a bit aggressive and continues to support the belief that prototypes may be seen in 2011 but full commercialization will not be seen till 2012)

Lu indicated that TSMC was developing 3D TSV technology with a broad focus on design, packaging and testing as well as the required foundry fabrication process. Lu indicated that n advances in design could help address current challenges related to process variations, thermal and mechanical stress.

Jang noted that design tools that work together seamlessly were required to “...speed the adoption of 3-D implementations”. Jang indicated that online video applications and mobile apps will require as much as 12.8 Gb/sec between I/O and memory with today's IC technology whereas 3-D packaging technology is expected to lower that by ~ 8X in Samsung DDRs.

Radojcic commented that 3D IC is "... not a one size fits all technology” and that it is essential to implement a Path Finding process up front in the system design in order to explore design options and make the right choices with respect to “technology, costs and die interactions”. As he has indicated at several other meetings recently [see IFTLE 11 “3D In and Around the Moscone Part 1”, Aug 2010] Radojcic feels that 3D IC ".. is all about managing choices” .

Marchal called 3D IC IMECs “man on the moon” program due to the long gestation period that was required to get all the necessary technologies into place. He prognosticated that 3D technology would arrive “ in the next two to three years," indicating that the technology has three main application drivers including “...convergence, high performance and memory systems."

DAC also held a tutorial entitled “3-D: New Dimensions in IC Design” which included instruction by Prof. Yuan Xie - Penn State, Prof. David Atienza - EPFL, Switzerland, Tanay Karnik – Intel, Paul Marchal – IMEC and Ruchir Puri - IBM .

As part of the conference the GSA (Global Semiconductor Association) held a 3D forum which reportedly had 125 attendees. Presentations were from major foundries, IDMs, EDA/IP vendors, design services and other industry organizations trying to accelerate 3D design.

For a short video of Lisa McIlrath of R3Logic discussing 3D design and design tools and their design tool “R3 Integrator” you can go here (link) .

The Global Semiconductor Alliance

In 2009 GSA’s EDA Interest Group, with representatives from EDA vendors, semiconductor firms, IC design services, research institutes and others decided to focus efforts on tools and flows to support the rapidly emerging 3-D/TSV technology. In the June 2010 issue of GSA forum, they addressed the benefits of 3D technology and described the results of an industry survey that they did on the subject.

While IFTLE agrees with their conclusion that “Accurate modeling tools and techniques, 3-D process design kits (PDKs), productive planning/partitioning tools, as well as 3-D-aware implementation and verification tools are needed. Design for 3-D testability is another challenge EDA needs to address.” Other comments like “Die stacks interconnected with TSVs are already in volume production (e.g., CMOS image sensors (CIS) in digital cameras and memory chips on top of each other to manufacture larger memory only configurations)” makes IFTLE wonder where they are getting their 3D technology industry status information. Oviously not from PFTLE or IFTLE ! for those readers know that while CIS do use TSV, they do not yet have stacked chips and while memory prototypes have been built with TSV, they are not yet commercial and certainly not is “volume production”

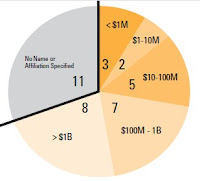

Lets look at some of the interesting survey conclusions that they reported. 36 semiconductor vendors responded. All expressed interest in 3-D/TSVs, and ~ 1/3 reported that they were already involved in ongoing 3-D/TSV R&D efforts. Eight of the 36 respondents are very large IC vendors, mostly fabless or fab-light, focused on the consumer and communications markets, and sell mixed-signal ICs. All achieved more than $1 billion in revenue in 2008. Seven companies generated between $100 million and $1 billion in revenue in 2008, and these companies design and manufacture mostly analog, RF and mixed-signal chips.

next week Part 3 of 3 concerning 3D activities at Semicon 2010.

For all the latest on 3D IC and advanced packaging stay linked to Insights From the Leading Edge...

Past PFTLE blogs are now available at www.pftle.net............

At the Atrenta booth they conducted live demonstrations of a working 3D design flow. The design flow addresses 3D-aware high-level synthesis, early partitioning, floorplanning and multi-domain analysis. The system is the result of on-going collaboration between Atrenta, AutoESL and Qualcomm.

TSMC and Cadence

In a joint announcement at DAC, TSMC and Cadence announced that Cadence 3D-IC implementation and integrated DFM have been incorporated into TSMC Reference Flow 11.0. (link). ST Juang, senior director of Design Infrastructure Marketing at TSMC noted that . “TSMC Reference Flow 11.0 enables 3D-IC integration to become part of the mainstream flow.” Advanced 3D design capabilities including physical design and implementation; RC extraction; analysis of timing, signal integrity, IR drop, electromagnetic and thermal analysis; and physical verification are included.

With this breakthrough year at DAC, IFTLE concurrs that “The time for 3D time is now !”

The Global Semiconductor Alliance

The Global Semiconductor Alliance was formed in 1994 as the “Fabless semiconductor Association”. Their goal is to focus on initiatives that will contribute to the growth and profitability of the semiconductor industry.

Lets look at some of the interesting survey conclusions that they reported. 36 semiconductor vendors responded. All expressed interest in 3-D/TSVs, and ~ 1/3 reported that they were already involved in ongoing 3-D/TSV R&D efforts. Eight of the 36 respondents are very large IC vendors, mostly fabless or fab-light, focused on the consumer and communications markets, and sell mixed-signal ICs. All achieved more than $1 billion in revenue in 2008. Seven companies generated between $100 million and $1 billion in revenue in 2008, and these companies design and manufacture mostly analog, RF and mixed-signal chips.

Mobile Internet devices (MIDs) are an obvious target segment to benefit from the space, power and cost savings that; 3-D/TSV offers. Cell phones were identified as the primary 3-D/TSV target application. Netbooks, Global Positioning System(GPS)systems and digital cameras were next in popularity.

Performance is the primary motivator for using this technology, while footprint , combined with board space savings, is a close second.

Practically all die stacks will contain at least one layer of memory.

There is also interest in integration of passives into the stack.

For all the latest on 3D IC and advanced packaging stay linked to Insights From the Leading Edge...

Past PFTLE blogs are now available at www.pftle.net............

Thursday, August 12, 2010

IFTLE 11 3D In and Around the Moscone Part 2

……….Continuing our look at the 3D related events at the recent Semicon West exhibition.

ITRI

The ITRI Ad-STAC program has been discussed previously [ see PFTLE 105 “Taiwanese Focus on 3D IC”, 11/06/2009; PFTLE 99 “3D IC at ITRI”,09/24/2009. At the Suss “3D Bonding and Thin Wafer Handling “ workshop Yu-Hua Chen, Deputy Div Director, announced that there is now a team of 150 fully engaged in 3D design, build and test.

Per their previous announcements they still appear to be on time to have their 300 mm 3D line qualified by the 4Q 2010 as shown below.

Their roadmap now shows CPU + RAM stacking and memory stacking in the 2011 / 2012 timeframe, in sinc with other Pacific rim foundries and assembly houses.

ITRI

The ITRI Ad-STAC program has been discussed previously [ see PFTLE 105 “Taiwanese Focus on 3D IC”, 11/06/2009; PFTLE 99 “3D IC at ITRI”,09/24/2009. At the Suss “3D Bonding and Thin Wafer Handling “ workshop Yu-Hua Chen, Deputy Div Director, announced that there is now a team of 150 fully engaged in 3D design, build and test.

Per their previous announcements they still appear to be on time to have their 300 mm 3D line qualified by the 4Q 2010 as shown below.

Their roadmap now shows CPU + RAM stacking and memory stacking in the 2011 / 2012 timeframe, in sinc with other Pacific rim foundries and assembly houses.

Suss

Wilfried Bair at his Suss “3D Bonding and Thin Wafer Handling “ workshop detailed the process module options for their temporary bond / debond cluster tool as shown below. He announced that their bonding chambers were now stackable to allow for smaller fab footprint. A detailed look at the Suss options has been given earlier [ see PFTLE 82 “SUSS MicroTec Bonders for Temporary and Permanent 3D Bonding Solutions”6/24/ 2009 and PFTLE 96 “Suss Microtec Thin Wafer Processing 3D IC Workshop”, 9/5/2009]

The Suss equipment is compatible with Brewer (thermal slide), 3M (laser release), HD (laser release) and TMAT (mechanical release) bond/debond processes which use different mechanics to debond the wafer from the carrier. As a result, the modules for debonding must be configured to the specific process conditions required by the adhesive.

Bair indicated that they have major wafer and interposer programs underway with both IMEC and ITRI.

Alchimer

Alchimer fresh off a cash infusion by the Panasonic Ventures Group (link) held a workshop looking a 3D status in general and their “fully wet” 3D process in particular. We have discussed their process in detail [ see PFTLE 124 “Major Moves by Alchimer “, 3/21/2010 and refs therein]

Sang Sok Lee – CEO of Lenix (Korean materials and equipment supplier to Samsung, Hynix and LG) announced the commercial availability of modular process equipment for running the Alchimer "fully wet” electrografting via fill process. The fully automated system was exclusively designed for the electro- grafting and chemical-Grafting used in the Alchimer solution. Modules include: isolation, barrier, Cu seed, via filling ( capable to 5 micron Via Diameter) and annealing.

Alchimer CTO Claudio Truzzi described the latest advances in their “fully wet” TSV line and fill process focusing on their ability to do high aspect ration TSV and their low COO.

Alchimer CTO (l) Claudio Truzzi and CEO (r) Steve Lerner

Truzzi announced that their CoO modeling using the Yole cost model shows that the wafer cost for the EMC-3D process is ~$250 per wafer vs the ~ $165 that EMC3D has previously reported (shown below) and that $70MM is needed for the equipment for such a line. We can surely expect a response from EMC3D shortly!

Yole Developpement

Jerome Baron of Yole presented their latest forcast which I have shown below by application. Their prediction that memory on logic will begin to become the driving application by 2013 is certainly consistent with current Foundry and OSAT roadmaps.

Baron offers the following (5) challenges for 3D IC to become mainstream;

- Infrastructure availability and supply chain - : availability of a second source 3D packaging service provider is critical… Additionally, key strategic alliances / partnerships between memory suppliers, Logic IDMs, Foundries and Packaging subcontractors need to be in place for 3D SiP applications involving multiple-party ICs (memory, logic, interposer…)

- I/O standardization between interfaces such as memory / logic / interposer layers is critical. Such specifications need to be defined in order to establish a standardized and flexible supply chain (e.g. of JEDEC initiative for defining LPDDR3 memory standards for 3D TSV in mobile applications)

- Thermal management and interconnect reliability: in many applications such as stacking of DRAM modules, SSD for enterprise market and memory + logic stacking applications, thermal management is certainly the biggest barrier to entry for 3D if we cannot manage to dissipate heat well through the whole package.

- Shift in the Design / Test method paradigm and system co-design: heterogeneous functions, packaging, new CAD tools (thermal and mechanical simulation), test for KGD and new design architectures are required to get the full benefits of 3D.

- and finally Cost: depending on end-product, 3D TSV manufacturing cost should be reasonable and reduced in order to make it widely occurring in cost sensitive applications.

Coming soon:

- 3D at the Design Automation Conference (DAC)

- Semicon coverage of EVG, Sematech, Novellus, Verigy

- SEMATECH 3D coverage at Semicon 2010

- A look at the new ITRS roadmaps

- A GSA survey on 3D IC …..and much more !

For all the latest in 3D IC and advanced packaging stay linked to Insights From the Leading Edge….

Friday, August 6, 2010

IFTLE 10 3D IC at the 2010 IEEE IITC

Coverage of Semicon 2010 will continue next week. I'm interrupting that coverage to make sure we don't forget to take a look at what occured at the IITC in June.

In 2008 PFTLE welcomed the IEEE IITC to the 3D IC bandwagon [ see PFTLE 37 “ IITC on the 3D Integration Bandwagon”,07/07/2008 ]. In each subsequent year they have continued to expand 3D IC coverage with quality papers as is shown below for their recent June 2010 meeting.

IMEC

IMEC gave several interesting presentations at the IITC. One paper focused on the high temperature characterization of TSV capacitance, leakage and resistance. They conclude that although TSV capacitance marginally increases with the increase in temperature, TSV depletion behavior can still be exploited to reduce TSV capacitance at higher temperatures. TSV leakage measurements show that TSV oxide integrity is preserved even at higher temperatures (150C). The increase in TSV resistance matches estimations based on the positive temperature coefficient of Cu resistivity. The limited impact of temperature on measured power-delay characteristics of 2D / 3D ring oscillator circuits is due to the increase of TSV capacitance.

Another paper examined the impact of TSV - transistor proximity. Copper filled TSVs (see figure below), with a diameter of 5.2 μm and a length (height) of 22 μm, were designed and fabricated close to MOSFETs. The impact of a single TSV was examined on both PMOS and NMOS with a channel length of 0.13 μm to ~0.15 μm. For each transistor, a TSV was placed next to its active region. The distance between the edge of the channel and the TSV varied from 1.1 to 1.6 μm.

All the MOSFETs with TSVs in close proximity demonstrated normal functionality. Compared to the transistors without TSVs in proximity, no performance degradation of key transistor parameters was identified. These results show that at a minimum distance of 1.1 μm from MOSFETs, the current TSV structure has little impact on the device operation in this technology. Transistors surrounded by multiple TSVs also revealed no significant performance shift in comparison to the control cases with no TSV.

Thermal cycling between -55 and 125ºC was applied to the stacked dies. After 1000 cycles, all devices were functional and no degradation was observed with TSV proximity.

IMEC concludes that the ‘middle-TSV’ approach implemented on 130-nm CMOS technology platform has no significant impact on the electrical operation of MOSFETs and demonstrates good long-term reliability but wisely cautions that depending on technology and layout, this might not always be the case. Similar conclusions were reached previously [ see PFTLE 122, “3D IC at the IEEE ISSCC”, 03/12/2010 ]

IMEC has shared information about using a polymer TSV insulation previously [ see PFTLE 125, “3D IC at Fort McDowell”, 03/28/2010 ] In their most recent presentation they detail the processing for backside TSV of 50 and proposes two separate constructions for 50 and 100 µm thicknesses, (a) vs (b), as shown in the figure below.

For the 100 um process, a chamfered shape is used to avoid stress buildup at the Si corner. A sloped cavity is first etched then a second a vertical etch is done using a Bosch process IE process. Then a spin-on-dielectric from JSR is used to conformally coat the TSV. Polymer is then removed from the bottom of the hole by litho and dry etching. They indicate that this process is less likely to scale since it needs a big enough hole to do litho at the bottom of it.

Possible dimensions for these two TSV construction options are shown below.

QUALCOMM

Gu of Qualcomm shared possible integration challenges for high volume production. The interesting figure below shows the Si area in mm2 lost due to occupancy of TSVs as a function of aspect ratio for 100 um thick Si. They conclude that to maintain low Si area penalty ( i.e 2 mm2), the TSV aspect ratio should be approx 10 for 10,000 vias. This is true, but assumes the requirement of a 100 µm Si thickness.

As you may know as a reader of PFTLE [ see PFTLE 68, “Like Swallows Returning to San Juan Capistrano”, 03/20/2009 and PFTLE 44, “Upcoming 3D Integration events; Issues with the ITRS 3D Roadmaps”,09/11/2008], this author prefers a thinner Si (i.e. 30 um) which would lead to 1/3 the AR for the same lost area. Given all other things being equal lower AR always will equal lower cost.

More interesting to IFTLE are the comments Gu makes about plasma damage, namely “If the TSV is connected to a transistor during processing (which they are once the TSV are exposed from the backside – IFTLE), the plasma charge from wafer backside may damage the device gate oxide on wafer front side. Protection diodes are usually employed to protect transistor from plasma charge in the wafer front side. However, backside plasma light can be blocked from reaching the front side diode, which makes the protection diode less effective. Minimizing the plasma charge on backside process is important.” Certainly something to keep in mind.

IBM

Emma of IBM has been thinking about 3D IC and how to use them for a very long time. At IITC he gave a very interesting perspective on where we are in 3D IC integration and where we should be going.

Emma contends that in most commercial cases today, 3D is simply a packaging technique used to simplify integration. That its principle applications have been in high-volume markets where the costs of assembly are most important (such as cameras and cell phones); in markets where the physical size of the end-product is fixed (e.g., DIMMs); and in markets where both the power density and the inter-chip signal density are low. He contends that the goals of these applications are to make the end products simpler by integrating multiple components into a single stack, thereby enabling a single package and simplifying the subsequent assembly processes. It provides a way to continue the density scaling for a given footprint.

....modularity

Modularity, Emma contends, can be one of the main advantages by providing a potentially simpler design flow. For example, large IP blocks (or even layers in disparate technologies from different vendors) can be incorporated into such a stack. This requires that there be well-defined interfaces, communication protocols, and technology ground-rules that will be common to all of the individual components (i.e. standardization) . He believes that the overheads associated with such well defined infrastructures, rules, and protocols are potentially lower than those required to compose the system using a traditional 2D approach.

This has the effect of “volumizing” those subsystems, which reduces their costs and their times-to-market. In addition, he proposes that 3D can allow clocking, power delivery and control, and test-related logic to be incorporated in a more modular way.

...bandwidth

Scaling through-silicon-via (TSV) size and pitch in 3D enables high bandwidth and low latency interconnects among multiple device layers. This can enable massive internal bandwidth.

He also suggests we need to be considering system applications in which”... the logical elements of a system can be physically co-located in the {x,y} dimensions so that unprecedented bandwidth in the {z} dimension can allow the stack to do types of computation that would not be fathomable in 2-space”.

When taking a look at the constraints of 3D IC Emma offers that when combining differently constrained layers into a stack, 3D integration “...will tend to impose the combined constraints on each individual layer. Among those constraints are: (i) a shared power envelope (the amount of current drawn in any layer can impact the other layers when there are shared Power/GND TSVs), (ii) a shared thermal envelope for heat removal, and (iii) interactions between the layers in the form of noise (the reduced distances in the vertical direction, especially in thinned silicon will exacerbate noise issues). While not a major problem in low power systems, the first two constraints can be quite challenging for high-power and high power-density applications, like microprocessors”

He concludes “Today, the obvious uses for 3D are the ones in which the costs, power, interconnectivity, and profit margins are all fairly low. 3D offers some clear advantages in the future integration of systems: better volumetric density, lower raw power, smaller component count, and better modularity. But realizing these advantages requires solving a new set of problems in (literally) a new dimension.”

3D IC at the Upcoming IEEE CICC

Trying to keep you updated on what’s coming as well as what has transpired, I would be remiss if I didn’t mention the upcoming design activities at the IEEE CICC (Custom Integrated Circuits Conf) sponsored by the Solid State Circuits (SSC) and Electron Device (ED) societies.

3D veteran Rakesh Patel, who is now working on 3D IC with Global Foundries, informs IFTLE that CICC will be addressing 3D from a design perspective in their upcoming Sept 19-22 meeting in San Jose [link]

Their 3D forum will include:

- “3D Integration Infrastructure: Requirements to Support High Volume Production”, W. R. Bottoms, Third Millennium Test Solutions

- “3D IC – TSV Micro-bump Modeling and Design Implementation Tools”, Vassilios Gerousis, Cadence,

- “3D Packaging Evolution from an OSAT Perspective”, Raj Pendse, STATS ChipPAC

- “Challenges and Emerging Solutions for Testing TSV-Based Three-Dimensional Stacked ICs”, Erik Jan Marinissen, IMEC

In addition session 15 entitled “3D Design Considerations” will address the major 3D design topics of the day.

For all the latest on 3D IC and advanced packaging stay linked to Insights From the Leading Edge, IFTLE.....................

....Past issues of PFTLE can be accessed at http://www.pftle.net/........

In 2008 PFTLE welcomed the IEEE IITC to the 3D IC bandwagon [ see PFTLE 37 “ IITC on the 3D Integration Bandwagon”,07/07/2008 ]. In each subsequent year they have continued to expand 3D IC coverage with quality papers as is shown below for their recent June 2010 meeting.

IMEC

IMEC gave several interesting presentations at the IITC. One paper focused on the high temperature characterization of TSV capacitance, leakage and resistance. They conclude that although TSV capacitance marginally increases with the increase in temperature, TSV depletion behavior can still be exploited to reduce TSV capacitance at higher temperatures. TSV leakage measurements show that TSV oxide integrity is preserved even at higher temperatures (150C). The increase in TSV resistance matches estimations based on the positive temperature coefficient of Cu resistivity. The limited impact of temperature on measured power-delay characteristics of 2D / 3D ring oscillator circuits is due to the increase of TSV capacitance.

Another paper examined the impact of TSV - transistor proximity. Copper filled TSVs (see figure below), with a diameter of 5.2 μm and a length (height) of 22 μm, were designed and fabricated close to MOSFETs. The impact of a single TSV was examined on both PMOS and NMOS with a channel length of 0.13 μm to ~0.15 μm. For each transistor, a TSV was placed next to its active region. The distance between the edge of the channel and the TSV varied from 1.1 to 1.6 μm.

Thermal cycling between -55 and 125ºC was applied to the stacked dies. After 1000 cycles, all devices were functional and no degradation was observed with TSV proximity.

IMEC concludes that the ‘middle-TSV’ approach implemented on 130-nm CMOS technology platform has no significant impact on the electrical operation of MOSFETs and demonstrates good long-term reliability but wisely cautions that depending on technology and layout, this might not always be the case. Similar conclusions were reached previously [ see PFTLE 122, “3D IC at the IEEE ISSCC”, 03/12/2010 ]

IMEC has shared information about using a polymer TSV insulation previously [ see PFTLE 125, “3D IC at Fort McDowell”, 03/28/2010 ] In their most recent presentation they detail the processing for backside TSV of 50 and proposes two separate constructions for 50 and 100 µm thicknesses, (a) vs (b), as shown in the figure below.

For the 50 μm process the wafers are attached to a temporary carrier and thinned down to 50 μm. 5 μm wide ring-shaped trenches are patterned on the wafer backside and etched through the Si substrate to the BEOL pre-metal dielectric (PMD) stack. The trenches are then filled with a spin-on dielectric material. Low viscosity materials are better at void free filling of the insulation trenches.

For the 100 um process, a chamfered shape is used to avoid stress buildup at the Si corner. A sloped cavity is first etched then a second a vertical etch is done using a Bosch process IE process. Then a spin-on-dielectric from JSR is used to conformally coat the TSV. Polymer is then removed from the bottom of the hole by litho and dry etching. They indicate that this process is less likely to scale since it needs a big enough hole to do litho at the bottom of it.

Possible dimensions for these two TSV construction options are shown below.

QUALCOMM

Gu of Qualcomm shared possible integration challenges for high volume production. The interesting figure below shows the Si area in mm2 lost due to occupancy of TSVs as a function of aspect ratio for 100 um thick Si. They conclude that to maintain low Si area penalty ( i.e 2 mm2), the TSV aspect ratio should be approx 10 for 10,000 vias. This is true, but assumes the requirement of a 100 µm Si thickness.

As you may know as a reader of PFTLE [ see PFTLE 68, “Like Swallows Returning to San Juan Capistrano”, 03/20/2009 and PFTLE 44, “Upcoming 3D Integration events; Issues with the ITRS 3D Roadmaps”,09/11/2008], this author prefers a thinner Si (i.e. 30 um) which would lead to 1/3 the AR for the same lost area. Given all other things being equal lower AR always will equal lower cost.

IBM

Emma of IBM has been thinking about 3D IC and how to use them for a very long time. At IITC he gave a very interesting perspective on where we are in 3D IC integration and where we should be going.

Emma contends that in most commercial cases today, 3D is simply a packaging technique used to simplify integration. That its principle applications have been in high-volume markets where the costs of assembly are most important (such as cameras and cell phones); in markets where the physical size of the end-product is fixed (e.g., DIMMs); and in markets where both the power density and the inter-chip signal density are low. He contends that the goals of these applications are to make the end products simpler by integrating multiple components into a single stack, thereby enabling a single package and simplifying the subsequent assembly processes. It provides a way to continue the density scaling for a given footprint.

....modularity

Modularity, Emma contends, can be one of the main advantages by providing a potentially simpler design flow. For example, large IP blocks (or even layers in disparate technologies from different vendors) can be incorporated into such a stack. This requires that there be well-defined interfaces, communication protocols, and technology ground-rules that will be common to all of the individual components (i.e. standardization) . He believes that the overheads associated with such well defined infrastructures, rules, and protocols are potentially lower than those required to compose the system using a traditional 2D approach.

This has the effect of “volumizing” those subsystems, which reduces their costs and their times-to-market. In addition, he proposes that 3D can allow clocking, power delivery and control, and test-related logic to be incorporated in a more modular way.

...bandwidth

Scaling through-silicon-via (TSV) size and pitch in 3D enables high bandwidth and low latency interconnects among multiple device layers. This can enable massive internal bandwidth.

He also suggests we need to be considering system applications in which”... the logical elements of a system can be physically co-located in the {x,y} dimensions so that unprecedented bandwidth in the {z} dimension can allow the stack to do types of computation that would not be fathomable in 2-space”.

When taking a look at the constraints of 3D IC Emma offers that when combining differently constrained layers into a stack, 3D integration “...will tend to impose the combined constraints on each individual layer. Among those constraints are: (i) a shared power envelope (the amount of current drawn in any layer can impact the other layers when there are shared Power/GND TSVs), (ii) a shared thermal envelope for heat removal, and (iii) interactions between the layers in the form of noise (the reduced distances in the vertical direction, especially in thinned silicon will exacerbate noise issues). While not a major problem in low power systems, the first two constraints can be quite challenging for high-power and high power-density applications, like microprocessors”

He concludes “Today, the obvious uses for 3D are the ones in which the costs, power, interconnectivity, and profit margins are all fairly low. 3D offers some clear advantages in the future integration of systems: better volumetric density, lower raw power, smaller component count, and better modularity. But realizing these advantages requires solving a new set of problems in (literally) a new dimension.”

3D IC at the Upcoming IEEE CICC

Trying to keep you updated on what’s coming as well as what has transpired, I would be remiss if I didn’t mention the upcoming design activities at the IEEE CICC (Custom Integrated Circuits Conf) sponsored by the Solid State Circuits (SSC) and Electron Device (ED) societies.

3D veteran Rakesh Patel, who is now working on 3D IC with Global Foundries, informs IFTLE that CICC will be addressing 3D from a design perspective in their upcoming Sept 19-22 meeting in San Jose [link]

Their 3D forum will include:

- “3D Integration Infrastructure: Requirements to Support High Volume Production”, W. R. Bottoms, Third Millennium Test Solutions

- “3D IC – TSV Micro-bump Modeling and Design Implementation Tools”, Vassilios Gerousis, Cadence,

- “3D Packaging Evolution from an OSAT Perspective”, Raj Pendse, STATS ChipPAC

- “Challenges and Emerging Solutions for Testing TSV-Based Three-Dimensional Stacked ICs”, Erik Jan Marinissen, IMEC

In addition session 15 entitled “3D Design Considerations” will address the major 3D design topics of the day.

For all the latest on 3D IC and advanced packaging stay linked to Insights From the Leading Edge, IFTLE.....................

....Past issues of PFTLE can be accessed at http://www.pftle.net/........

Sunday, August 1, 2010

IFTLE 9 3D In & Around the Moscone Part 1

I’ve seen reports of “crowded exhibit floors making it difficult to meet with companies” at Semicon West. Not sure what meeting these folks were at ? Maybe that was true in the building housing photovoltaics. As someone who has been coming to Semicon West for ~25 years I saw fewer booths and fewer attendees, fewer even then last year. Certainly nothing like the congestion that existed 10-20 years ago. I personally think we are seeing the gradual impact of our industry moving off shore. US industry is simply not as relevant as we were 20 years ago in microelectronics and there are far fewer of us in the US to attend such trade shows.

IC Insights

Bill McClean, who correctly predicted the 2010 bull electronics market in March of 2009 [see PFTLE 67 “IC Insights Predicts Fast Industry Rebound at IMAPS Global Business Council”,3/15/2009 ] stated that Samsung is now spending 20% of the worlds electronics capex (~ 10B$). He sees the next downturn coming in 2013 and does not see 450 mm wafers coming till post 2015.

Proteus Biomedical

Proteus biomedical CEO Andrew Thompson during his presentartion on how microeletronics was going to affect the medical community shared the remarkable fact that the earths 7B people only 3B of them have a pair of shoes but there are 5B cell phone subscribers! That’s a lot of barefoot people talking on the phone! Another interesting

GlobalFoundries

Gregg Bartlett, Sr VP of Technology and R&D in his plenary presentation on “The Centrality of Silicon” showed 3D IC becoming essential at the 22 nm node as shown below.

Qualcomm

Qualcomm has become one of the strongest corporate advocates for 3D IC in the world. For some of their recent activity see [PFTLE 126 “Adv Pkging at the IMAPS Device Pkging Conf”, 04/01/2010; PFTLE 125 “3D IC at Ft McDowell”, 03/27/2010 ].

At the TechXSpots “Bridging the Gap” session Steve Bezuk of Qualcomm shared his views on how 3D fits into mobile device roadmaps. Bezuk’s comment that “The constraints of the low power, mobile market present no fundamental technical barriers to 3D TSV technologies” was music to a 3D advocates ears.

He used the PFTLE “4 Horseman of the apocalypse” concept [ see PTFLE 102, “The 4 Horsemen of 3D IC”, 10/16/2009 to make his point as seen below. He notes that:

- for the heterogeneous stacking designs that they are looking at today, 2D tools appear to suffice

- no thermal issues have been uncovered that do not alreadyexist for todays 2D designs

- todays sophisticated SoC test proceedures looks thik they can do he job for entry level 3D products

Qualcomms Riko Radojcic, speaking at the Alchimer 3D workshop, echoed the earlier remarks of Steve Bezuk that Qualcomm can “manage the current design flow using current EDA products”. Riko, as a designer, indicated that 3D IC was a matter of managing choices and interactions (which are listed below) .

Riko indicated that thermal and mechanical stress considerations need to be incorporated into design enablement and stack design signoff.

ASE

Calvin Cheung at the Suss “3D Bonding and Thin Wafer Handling “ workshop indicated that ASE sees consumer markets driving the roadmaps towards 3D IC. Cheung indicated that facial recognition and bio-sensing for medical diagnostics were two applications that customers have indicated would be highly desirable if integrated on their PDAs.

During a panel Q&A session Chueng indicated that TSMC will be driving the initial use of interposers and that ASE was on board. “We will need interposers to bond 28 nm low K die…right now it is impossible to stack such mechanically unstable materials into a stable 3D stack” Cheung also sees interposers serving as a platform for IPD (integrated passive devices) which will allow them to get decoupling caps closer to where they are needed and that “Graphics chip sets will also require solutions where the power is not channeled through the memory”, making them another potential application for interposers. At least for the first generation products.

Rich Rice from ASE at the Bridging the Gap TechXSpot, presented the following IC cost breakdown from a recent Prismark report which indicates that Packaging and assembly constitutes 16% of total shipped silicon cost.

Amkor

Bob Lanzone, at the Suss “3D Bonding and Thin Wafer Handling “ workshop indicated that Amkor is now focusing heavily on the unit operations required to handle TSV middle wafers from foundries. They have backed off their focus on backside TSV fabrication which Bob feels is well under control. Bob says that F2F (face-to-face) CoC (chip-on-chip) technology has been qualified with Cu/Sn IMC down to 40 um pitch. Below 40 um he feels Amkor will move to some form of direct Cu-Cu bonding.

Coming soon:

- 3D IC at the IEEE IITC

- Semicon coverage of Suss, Alchimer, Yole, ITRI, EVG, Sematech, Novellus, Verigy

- 3D at the design automation conference

- A look at the ITRS new roadmap…..and much more

For all the latest in 3D IC and advanced packaging stay linked to Insights From the Leading Edge...

For past PFTLE blogs go to www.pftle.net)

Having said that, the 3DIC activity was significant. There were two days of sessions led by Sematech, a workshop held by Alchimer, a workshop by Suss and Semicon TechXSpots sessions such as “Bridging the Gap”. We’’ll cover all of that and more, here at IFTLE,over the next few weeks.

Bill McClean, who correctly predicted the 2010 bull electronics market in March of 2009 [see PFTLE 67 “IC Insights Predicts Fast Industry Rebound at IMAPS Global Business Council”,3/15/2009 ] stated that Samsung is now spending 20% of the worlds electronics capex (~ 10B$). He sees the next downturn coming in 2013 and does not see 450 mm wafers coming till post 2015.

Proteus Biomedical

Proteus biomedical CEO Andrew Thompson during his presentartion on how microeletronics was going to affect the medical community shared the remarkable fact that the earths 7B people only 3B of them have a pair of shoes but there are 5B cell phone subscribers! That’s a lot of barefoot people talking on the phone! Another interesting

GlobalFoundries

Gregg Bartlett, Sr VP of Technology and R&D in his plenary presentation on “The Centrality of Silicon” showed 3D IC becoming essential at the 22 nm node as shown below.

Qualcomm has become one of the strongest corporate advocates for 3D IC in the world. For some of their recent activity see [PFTLE 126 “Adv Pkging at the IMAPS Device Pkging Conf”, 04/01/2010; PFTLE 125 “3D IC at Ft McDowell”, 03/27/2010 ].

At the TechXSpots “Bridging the Gap” session Steve Bezuk of Qualcomm shared his views on how 3D fits into mobile device roadmaps. Bezuk’s comment that “The constraints of the low power, mobile market present no fundamental technical barriers to 3D TSV technologies” was music to a 3D advocates ears.

He used the PFTLE “4 Horseman of the apocalypse” concept [ see PTFLE 102, “The 4 Horsemen of 3D IC”, 10/16/2009 to make his point as seen below. He notes that:

- for the heterogeneous stacking designs that they are looking at today, 2D tools appear to suffice

- no thermal issues have been uncovered that do not alreadyexist for todays 2D designs

- todays sophisticated SoC test proceedures looks thik they can do he job for entry level 3D products

Bezuk added that Qualcomm is focused on copper vias middle and that detailed Qualcomm cost models are showing that the cost adder for 3D at 45 and nm should be ~ 10%.

Qualcomms Riko Radojcic, speaking at the Alchimer 3D workshop, echoed the earlier remarks of Steve Bezuk that Qualcomm can “manage the current design flow using current EDA products”. Riko, as a designer, indicated that 3D IC was a matter of managing choices and interactions (which are listed below) .

ASE

Calvin Cheung at the Suss “3D Bonding and Thin Wafer Handling “ workshop indicated that ASE sees consumer markets driving the roadmaps towards 3D IC. Cheung indicated that facial recognition and bio-sensing for medical diagnostics were two applications that customers have indicated would be highly desirable if integrated on their PDAs.

During a panel Q&A session Chueng indicated that TSMC will be driving the initial use of interposers and that ASE was on board. “We will need interposers to bond 28 nm low K die…right now it is impossible to stack such mechanically unstable materials into a stable 3D stack” Cheung also sees interposers serving as a platform for IPD (integrated passive devices) which will allow them to get decoupling caps closer to where they are needed and that “Graphics chip sets will also require solutions where the power is not channeled through the memory”, making them another potential application for interposers. At least for the first generation products.

Rich Rice from ASE at the Bridging the Gap TechXSpot, presented the following IC cost breakdown from a recent Prismark report which indicates that Packaging and assembly constitutes 16% of total shipped silicon cost.

Bob Lanzone, at the Suss “3D Bonding and Thin Wafer Handling “ workshop indicated that Amkor is now focusing heavily on the unit operations required to handle TSV middle wafers from foundries. They have backed off their focus on backside TSV fabrication which Bob feels is well under control. Bob says that F2F (face-to-face) CoC (chip-on-chip) technology has been qualified with Cu/Sn IMC down to 40 um pitch. Below 40 um he feels Amkor will move to some form of direct Cu-Cu bonding.

Coming soon:

- 3D IC at the IEEE IITC

- Semicon coverage of Suss, Alchimer, Yole, ITRI, EVG, Sematech, Novellus, Verigy

- 3D at the design automation conference

- A look at the ITRS new roadmap…..and much more

For all the latest in 3D IC and advanced packaging stay linked to Insights From the Leading Edge...

For past PFTLE blogs go to www.pftle.net)

Subscribe to:

Comments (Atom)